#### CHAPTER 8

# OVERVIEW OF EMBEDDED SOC SYSTEMS

The remainder of the book applies the basic hardware design techniques learned in Part I to develop a simple and functional *embedded SoC* (System on a Chip) that contains a video subsystem and a memory-mapped I/O subsystem with general-purpose peripherals, customized hardware accelerators, and a music synthesizer. Our study is still focusing on the hardware design, but within the context of SoC, and it introduces many important design concepts, such as hardware acceleration, bus interface, and software drivers, along the way. In this chapter, we introduce the concept of an embedded SoC, discuss the development flow, explain the simple SoC framework used in this book, and provide an overview of Parts II, III, and IV.

#### 8.1 EMBEDDED SOC

#### 8.1.1 Overview of embedded systems

An embedded system (or embedded computer system) can be loosely defined as a computer system designed to perform one or a few specific tasks. The computer system is not the end product but a dedicated "embedded" part of a larger system that often includes additional electronic and mechanical parts. By contrast, a general-purpose computer system, such as a PC (personal computer), is a general computing platform and itself is the end product. We refer to it as a desktop-like computer system in the book. A desktop-like system is designed to be flexible and

to support a variety of end-user needs. Application programs are developed based on the available resources of the general-purpose computer system.

Embedded systems are used in a wide range of applications and each application has its own specific requirements. On one hand, a "low-end" system, such as a microwave oven, involves only a simple control function and can be implemented by an 8-bit single-chip microcontroller. On the other hand, a "high-end" system, such as a digital camera, is more complex. It performs two major tasks. The first task involves the general "housekeeping" I/O operations, including processing the button and knob activities, generating a menu on an LCD display, and writing image files to the storage device. These operations are more involved than those of a microwave oven and the system requires a more capable processor. The second task is to process the image and perform data compression to reduce the file size. Because of the large number of pixels and the complexity of the compression algorithm, the task requires a significant amount of computation. An embedded processor is usually not powerful enough to handle the computation-intensive operation. A custom digital circuit, sometimes known as a hardware accelerator, can be designed to perform this particular task and take the load off the processor.

#### 8.1.2 FPGA-based SoC

A "high-end" embedded system usually has a processor and simple I/O peripherals to perform general user interface and housekeeping tasks and special hardware accelerators to handle computation-intensive operations. These components can be integrated into a single integrated circuit, commonly referred to as an *SoC* (system on a chip).

As the capacity of FPGA devices continues to grow, the same design methodology can be realized in an FPGA chip. Instead of just realizing the system functionalities by customized software, we can incorporate customized hardware into the embedded system as well. The FPGA technology allows us to tailor the processor, select only the needed I/O peripherals, create a custom I/O interface, and develop specialized hardware accelerators for computation-intensive tasks. The FPGA embedded system provides a new dimension of flexibility because both the hardware and software can be customized to match specific needs. The methodology of exploiting the trade-offs between hardware and software and developing and integrating them concurrently is referred to as hardware-software co-design.

#### 8.1.3 IP cores

In SoC development, systems frequently have certain common functionalities and the same building blocks can be reused in different designs. These components are known as *IP* (intellectual property) cores, or simply as *IPs*. They are somewhat like functions in a software library, which can be used in different application programs. The IP cores can be developed by the device manufacturers, third-party vendors, or the users themselves. Unlike software functions, FPGA vendor's IP cores are usually tailored for their own proprietary platforms. They are not portable and frequently delivered as "black boxes" (i.e., without HDL source codes). For example, all companies provide FFT (fast Fourier transform) IP cores. While the cores perform similar functions, their interfaces, timing characteristics, and configuration

procedure are different. Therefore, a system must be redesigned or modified if it is re-targeted to a device from a different vendor.

#### 8.2 DEVELOPMENT FLOW OF THE EMBEDDED SOC

The embedded SoC design consists of the following tasks:

- Partition the tasks to software routines and hardware accelerators.

- Design user custom IP cores if needed.

- Develop the hardware.

- Develop the software.

- Implement the hardware and software and perform testing.

These tasks are discussed in the following subsections.

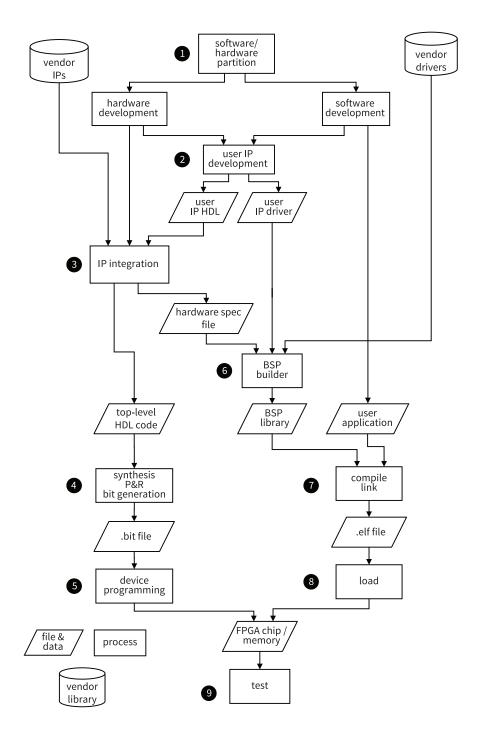

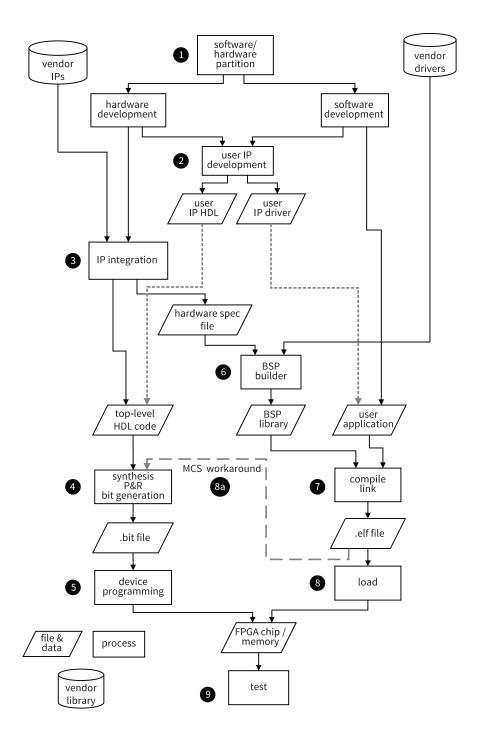

Because of the complexity of modern digital systems, pre-designed IP cores are used extensively in SoC development. Each vendor has its own IP framework, which provides a comprehensive collection of IP cores and supporting software device drivers. The development flow is frequently centered on the IP cores and is shown in Figure 8.1.

#### 8.2.1 Hardware-software partition

Step 1 (labeled 1 in the diagram) is to determine the software—hardware partition. An embedded application usually performs a collection of tasks. In an SoC-based design, a task can be implemented by hardware, software, or both. Based on the performance requirement, complexity, and hardware core availability, we can decide the type of implementation accordingly.

In an ideal scenario, the vendor IP library contains all the needed IP cores for the SoC design. However, in reality, most designs require a certain number of custom IP cores for hardware accelerators and special I/O peripherals. Step 2 is to develop the hardware codes and the corresponding software drivers of these custom IP cores. The details are discussed in Subsection 8.2.5.

#### 8.2.2 Hardware development flow

The left branch represents the hardware design flow. Step 3 is to utilize and integrate the IP cores to construct the system. In Vivado Design Suite, it is done by the IP integrator utility. A user can select IP cores, configure them with the desired characteristics, and connect the cores with a proper interface. IP Integrator will invoke the cores from the library and generate the HDL codes. The top-level HDL file usually resembles the top-level block diagram of an SoC design. During the generation, IP Integrator also produces an auxiliary hardware platform specification file, which contains the "definition" of the SoC design, including the processor configuration, memory size and structure, I/O peripheral cores used, memory address mapping, etc.

The top-level HDL file can be treated as a normal HDL file and processed accordingly. Steps 4 and 5 perform synthesis and placement and routing and eventually generate the FPGA configuration file (i.e., the .bit file).

Figure 8.1 IP-centered SoC development flow

#### 8.2.3 Software development flow

The right branch represents the software design flow. A top-level software program usually contains two types of codes. One type is the "system codes," which are pre-designed and provided with the system. They can be functions from libraries, service routines from the operating system, etc. The other type is the "application codes," which are developed by the user to perform the custom tasks. These system functions and service routines are called by the application codes.

In an embedded system, a BSP (board support package) is a mechanism to encapsulate the system codes. Since an embedded system is designed to perform a specific task, each system has a different memory structure and contains a unique set of I/O peripherals. BSP is a customized collection of device drivers and initialization routines that support a particular system. The term "board" is used since earlier embedded systems were implemented in a printed circuit board rather than a single silicon device.

An important ingredient of a BSP is the *device drivers*. A device driver is a set of routines that operate or control a particular peripheral device. A driver acts as a "translator" between the hardware peripheral and application programs and enables the application programs to access peripheral functions without needing to know precise details. If an IP core is expected to interface with a processor, a device driver should be developed concurrently.

The embedded SoC flow adopts the BSP mechanism. Step 6 is to build the BSP according to the SoC hardware configuration. Recall that, in Step 3, IP integrator generates a hardware platform specification file. The BSP builder utility examines the IP core information, extracts the pre-build device drivers and initialization routines from the vendor software library, and creates the BSP for the specific SoC design.

The application program can invoke the driver routines in the BSP to access the peripheral I/O cores. Step 7 compiles and links the software routines and BSP library and builds the final software image file (i.e., the .elf file).

#### 8.2.4 Physical implementation and test

Physically implementing the system involves two steps. We first download the FPGA configuration file to the FPGA device (i.e., "program" the device), as in Step 5, and then load the software image into processor's main memory, as in Step 8. The physical system can be tested afterward, as in Step 9.

#### 8.2.5 Custom IP core development

Although FPGA vendors provide a comprehensive collection of pre-designed IP cores, they seldom can cover all the project needs. We usually have to design custom IP cores for special I/O peripherals or less common computation algorithms. The development consists of three tasks:

- Design a custom digital circuit to implement the computation algorithm or special functionality.

- Derive an interface to connect the circuit to the bus or interconnect structure of the vendor's IP framework.

• Develop a device driver to control the new hardware core and integrate it into vendor's software library.

Note that the latter two activities depend on the FPGA vender's IP platform. We need to carefully study the platform's interface protocols and driver structure so that the IP core can be integrated into vendor's framework and used in the IP integration utility. Since each vendor has its own proprietary IP platform, the interface and driver are not portable and must be re-designed for each vendor.

#### 8.3 FPRO SOC PLATFORM

#### 8.3.1 Motivations

While the embedded SoC is powerful methodology, it is not the emphasis of this book. First and foremost, this book focuses on the register-transfer level hardware design rather than the system-level analysis and integration. In addition, a commercial IP platform is not ideal for learning introductory hardware design for several reasons:

- A commercial IP platform is quite complex and thus a significant amount of time will be spent on learning to use the tool rather than doing design.

- Most commercial IP cores are provided as black boxes.

- The interface protocol and driver structure are quite complex.

- The IP framework is proprietary. Thus, learning is tied to a particular platform and the developed IP cores are not portable.

In this book, we define a simple SoC platform and call it *FPro SoC*, (which is abbreviated from the book title "<u>FPGA Prototyping</u>" or can be interpreted as "<u>F</u>un and <u>Professional</u>"). It contains a video subsystem and a memory-mapped I/O subsystem with general-purpose peripherals, customized hardware accelerators, and a music synthesizer. Our study is still focusing on the hardware design but within the SoC context. The main characteristics of the FPro SoC platform are as follows:

- Simple. The FPro SoC platform defines a simple synchronous bus protocol and a straightforward device driver structure. Once a hardware circuit is developed, it can be converted to an IP core by adding a simple interface circuit and a device driver. The core then can be incorporated into the existing embedded system.

- Functional. FPro SoC platform provides a variety of I/O peripherals and commonly used serial interfaces (UART, SPI, and I<sup>2</sup>C) and includes working device drivers. It resembles a bare-metal 32-bit microprocessor board and can implement real-world projects targeted for this type of boards.

- Portable. Except for the processor, FPro SoC's IP cores are developed from scratch in HDL and do not use any vendor's proprietary components. The bus protocol and device drivers are not tied to any specific commercial platform, either. Thus, the IP cores and software codes are portable and can be reused for different FPGA devices and prototyping boards.

- "Upward compatible." While the FPro SoC platform is simple, the development follows rigorous and proven design principles and practices. These knowledge and skills can be applied in the future for more complicated commercial platforms and larger projects. In fact, the IP cores and drivers development

oped can be easily modified to be incorporated into existing commercial IP frameworks.

• Fun. Because the developed system is like a real microprocessor board, it can incorporate existing I/O modules and quickly develop a functional prototyping project. In addition, this platform can provide hardware acceleration capability and thus is more capable and more flexible than any microprocessor board. This give us an opportunity to develop interesting and challenging projects and make studying hardware more "fun" rather than "learning hardware for the sake of hardware."

#### 8.3.2 Platform hardware organization

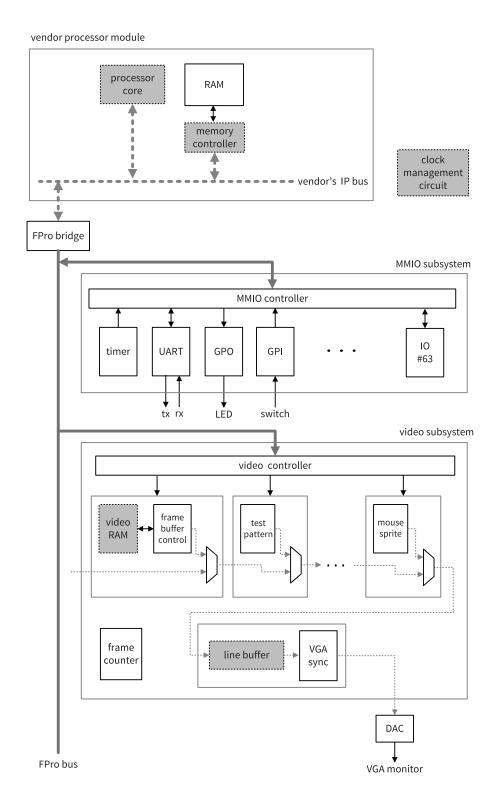

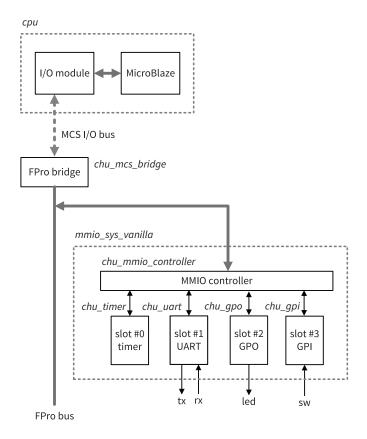

The top-level diagram of an FPro system is shown in Figure 8.2. It is composed of four major parts:

- Processor module

- FPro bridge and FPro bus

- MMIO (memory mapped I/O) subsystem

- Video subsystem

We only use vendor's IP cores for the processor, memory controller, line buffer, and clock management circuit, which are shown as dotted gray boxes in the figure, and construct all other cores from scratch.

*Processor module* The processor module consists of a processor, a memory controller core, and RAM. It is the part that is constructed from the vendor's IP cores. To be used in the FPro SoC platform, the processor core must exhibit the following characteristics:

- 32-bit-wide data path

- 32-bit memory address space

- Memory-mapped-I/O scheme for I/O access

Almost all FPGA-based processors support these features. There is no restriction on types of RAM. It can be FPGA's internal memory modules or external memory devices. However, since an FPro system resembles an entry-level 32-bit embedded system, we assume that the size of RAM is limited and software is developed in this context.

FPro bridge and FPro bus The processor needs to communicate with other cores. This is done by a bus or interconnect structure specified in the vendor's IP platform. The modern interconnect is designed to accommodate a wide variety of communication and data transfer needs and involves complex protocols. For our learning purposes, we define a simple synchronous bus protocol for the two subsystems and call it FPro bus. The FPro bridge converts vendor's native bus signals into FPro bus signals. The FPro bus protocol and bridge are discussed in Chapter 10.

MMIO subsystem In the memory-mapped-I/O scheme, the memory and registers of the I/O peripherals are mapped to the same address space. This means that the processor makes no distinction between the memory and I/O peripherals and uses the same read and write instructions to access the I/O peripherals.

The MMIO subsystem provides a framework to accommodate memory-mapped general-purpose and special I/O peripherals as well as hardware accelerators. For

Figure 8.2 Top-level diagram of an FPro system

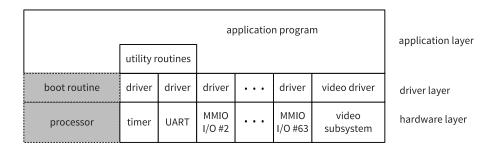

Figure 8.3 Software hierarchy of an FPro SoC system

simplicity, we define a standard *slot interface* that conforms to the FPro bus protocol. The MMIO subsystem consists of a controller to select a specific slot and can accommodate up to 64 instantiated cores. After being "wrapped" with an interface circuit, custom digital logic can be plugged into the FPro platform. About a dozen IP cores are developed and integrated into the MMIO subsystem in the subsequent chapters.

Video subsystem The video subsystem establishes a framework to coordinate the operation of video cores. A video core generates or processes the video data stream. The cores are arranged as a cascading chain. The data stream is pipelined and "blended" through each stage and eventually displayed on a VGA monitor. The video subsystem demonstrates the principles of handling stream data, in which data are generated continuously and passed through a chain of components for processing.

#### 8.3.3 Platform software organization

Since the book focuses on hardware design, we use a simple *bare metal* software scheme for the system. A bare metal system contains no operating system. In its simplest form, the processor boots directly into an infinite main loop, which contains functions to check input, perform computation, and write outputs.

The software hierarchy of an FPro system is shown in Figure 8.3. It contains a hardware layer, a driver layer, and an application layer. A boot routine is associated with the processor. It first performs the basic initialization process, such as clearing the caches, configuring the stack and heap segments, and initializing the interrupt, and then transfers control to the main program. The codes are obtained from the vendor, as shown in a dotted gray box in the figure. All other device drivers are constructed from scratch.

To facilitate the software development, we develop several simple utility routines that maintain a system time and assist displaying a debug message on the console. The timer core and UART (universal asynchronous receiver and transmitter) core in slots 0 and 1 are used for this purpose, as shown in Figure 8.2. Thus, the two cores should always be instantiated in the first two slots and not be replaced.

Every I/O core in the FPro system is accompanied by a driver. We select C++ for driver development because of its support of data encapsulation. A C++ class will be created for each core.

Except for accessing system time (via a timer core) and sending debugging messages (via a UART core), a class is largely "self-contained" and does not interact with other classes. When a core is attached or removed from an FPro system, the corresponding driver files should be included or deleted from the software projects. In the main application program, an instance will be created for each instantiated IP core and the methods in the class will be used to access and control the core. The "state" of the core, if existing, is kept within the private section of the instantiated object and involves no external variables.

#### 8.3.4 Modified development flow

The original development flow shown in Figure 8.1 needs to be revised to accommodate the FPro SoC platform. While the basic procedure remains unchanged, we need to manually construct the top-level HDL code and manually include the device driver files in our software application. The modified flow is shown in Figure 8.4 and the new paths are highlighted as thick gray dotted lines in the top half. The main changes are as follows:

- In Step 3, only the processor module, which contains a processor core and RAM, is generated via the IP integration utility. We must manually construct the HDL code for the top-level system, which is composed of the instantiation of the previously generated processor module and the MMIO and video subsystems from Step 2.

- In Step 6, since only the processor module configuration is listed in the hardware specification file, only processor-related codes, such as the boot routine, will be included in the BSP library. We must manually examine the IP cores in the top-level HDL file and include the corresponding driver files in the application software project.

- Since the processor module is the same most of the time, Steps 1 and 6 only need to be executed once. The generated HDL files and BSP library can be use in subsequent designs.

#### 8.4 ADAPTATION ON THE DIGILENT NEXYS 4 DDR BOARD

The book uses the Digilent Nexys 4 DDR prototyping board, which is designed around the Xilinx Artix 7 XC7A100T device, for the experiments and projects. Xilinx provides a soft-core processor, known as *MicroBlaze*, as well as a completely "pre-configured" system, known as *MicroBlaze MCS* (for *MicroBlaze Micro Controller System*). We select MCS as the processor module in Figure 8.2.

MicroBlaze is a 32-bit FPGA-based processor with RISC (reduced instruction set computer) architecture. It is highly configurable and can incorporate an optional floating-point unit, instruction and data caches, a memory management unit, etc. MicroBlaze mainly uses the AXI (Advanced eXtensible Interface) protocols from ARM to interface with other IP cores. Hundreds of IPs from Xilinx and third-party vendors, including memory controllers, I/O peripherals, and various types of hardware accelerators, can be integrated with a MicroBlaze to form an SoC design. The flow in Figure 8.1 is targeted for this type of setting.

MicroBlaze MCS is a *complete computer system* that is composed of a preconfigured MicroBlaze processor, a RAM constructed with FPGA's internal mem-

Figure 8.4 FPro SoC development flow

ory, and an I/O module with a standard set of microcontroller peripherals. MicroBlaze MCS provides only a limited degree of configurability. A user can set the size of RAM (between 8 KB and 128 KB) and select a small set of simple I/O peripherals.

Since the focus of the book is hardware design rather than system-level integration, MicroBlaze MCS serves the purpose very well. In addition, many simpler prototyping boards use Xilinx's earlier Spartan devices and must use ISE WebPack for development. At the time of writing, MicroBlaze MCS is free across all Xilinx platforms, including both the ISE WebPack edition and Vivado WebPack edition, but the full-featured MicroBlaze processor is only free for the Vivado WebPack edition. Thus, MicroBlaze MCS can be adopted by more entry-level prototyping boards.

On the down side, support for MicroBlaze MCS is not as comprehensive. The Vivado 2016 edition is used at the time of writing. Step 8 in Figure 8.4 does not function properly. The workaround is to associate the .elf file as the "initial values" of FPGA's internal memory and regenerate the configuration file (i.e., .bit file). The approach is shown as a thick dashed line in the bottom of Figure 8.4. The revised flow becomes:

- Develop and implement hardware (Steps 1 to 4).

- Develop and implement software (Steps 2 to 7).

- Associate the .elf file in the hardware project (Step 8a.).

- Regenerate the configuration .bit file with the embedded .elf file (i.e., repeating Step 4).

- Program the FPGA device and perform testing (Steps 5 and 9).

This flow is less ideal since regenerating the .bit file for each software revision is time-consuming and Vivado software must be invoked during software development.

XC7A100T is a fairly large device and its internal memory modules can accommodate 128 KB RAM for MicroBlaze MCS and 350 KB video RAM for a 9-bit VGA frame buffer. Thus, no external memory device is involved.

#### 8.5 PORTABILITY

A main goal of this book is to develop a portable system to learn hardware design and to introduce SoC practice. Because of the proprietary development software, the IP platform, and IP cores, it is difficult to construct a complete device- and board-independent FPGA-based SoC system. The experiments and projects in this book are constructed and tested on a specific board (Digilent Nexys 4 DDR) that contains a specific FPGA device (Xilinx Artix 7 XC7A100T). The following subsections discuss portability issues.

#### 8.5.1 Processor module and bridge

Since the processor module is constructed from the vendor's proprietary IP cores, it potentially introduces several portability issues:

- Processor

- Memory controller and RAM

- Interface and bridge

- Loading and booting of software

The FPro platform basically requires a 32-bit processor core that supports memory-mapped I/O scheme. Almost all FPGA-based processors satisfy this requirement. The internal and external memory sizes and configurations can vary significantly among different FPGA devices and prototyping boards. However, since the RAM inside the processor module only interacts with the processor core, it does not affect the subsystems directly. In summary, although the proprietary and different memory configurations are used in the processor module, they will not cause serious compatibility issues. The simplest way to create the processor modules is to utilize FPGA's internal memory, as in MicroBlaze MCS. However, older and simpler FPGA devices provide less internal memory. MicroBlaze MCS can be configured with smaller RAM. The size of the RAM, of course, sets the limit on the size of application program.

The FPro bus protocol is designed for simple non-burst synchronous read and write transactions. It can be considered as a very small subset of existing full-featured bus interfaces. Designing a bridge is not very difficult.

While compiling and linking the software code follows a similar tool chain, there is no standard procedure to load an .elf file (Step 8 in the development flow). The process depends on the device, memory configuration, prototyping board, and software development platform. We need to consult the specific manual or user guide to complete this task.

#### 8.5.2 MMIO subsystem

Since the MMIO subsystem's controller and the attached IP cores are constructed from scratch and use no vendor's proprietary IPs or components, the HDL codes are completely portable. They can be implemented as long as a prototyping board has adequate external peripherals. The only exception is the Artix's built-in ADC (analog to digital converter), known as XADC, which is only available for newer Xilinx devices.

Since the Nexys 4 DDR board contains all the needed peripherals, all MMIO IP cores can be implemented and tested without any external component. Some peripherals may not be available on other prototyping boards. However, the external circuitries are quite simple and can be easily implemented on a breadboard. The schematics for these peripherals can be found in the Nexys 4 DDR on-line manual and reconstructed accordingly.

#### 8.5.3 Video subsystem

While the majority of the video subsystem is designed from scratch, three components – clock management circuit, line buffer, and frame buffer – utilize vendor's proprietary IP cores. The clock management circuit and line buffer accommodate the VGA synchronization, whose clock rate is different from system clock rate. The former requires a PLL (phase-locked loop) like macro cell and the latter is based on a dual-clock FIFO buffer macro cell. Although these macro cells are proprietary, they are common and can be found in all FPGA devices. The proper macro cells can be instantiated in HDL code directly. Thus, the clock management circuit and line buffer do not lead to serious portability issues.

The frame buffer tends to be the most troublesome and least portable IP core in the FPro framework. The key part of the frame buffer is a dual-port memory that is accessed by the processor and frame control. The latter retrieves data from memory and converts the data into a video stream. The buffer requires a substantial amount of RAM and thus should be implemented by external memory devices. This raises several issues:

- FPGA prototyping boards have different types of memory devices and configurations and some simpler boards may have none.

- Except for simple SRAM devices, a sophisticated proprietary memory controller IP core is needed.

- The frame buffer control must interface with the proprietary memory controller and implement the dual-port access control circuit.

- The same external memory device may be used as processor's RAM and frame buffer at the same time. The partition further complicates the interface and configuration.

Thus, it is difficult to construct a portable frame buffer.

To demonstrate the design principle, the book uses FPGA's internal memory for the video memory. 350 KB of internal RAM is allocated for a frame buffer with a 9-bit VGA resolution. This is doable because the Nexys 4 DDR board contain a large XC7A100T device. It cannot be duplicated in boards with smaller devices. One possible alternative is to reduce the color depth from 9 bits to 1 bit.

Some advanced prototyping boards use HDMI port for the video output. Instead of using a DAC to generate the analog signal, the HDMI interface encodes the output from the line buffer, "serializes" the data, and transmits the video signal digitally through three serial lines. Thus, additional circuits must be added to accommodate the new interface.

#### 8.6 ORGANIZATION

The remaining book consists of three parts. The rest of Part II provides an overview of the hardware architecture and the bare metal embedded software development via the construction of the *vanilla FPro system*, which contains a timer core, a UART core, a GPI (general-purpose input) core, and a GPO (general-purpose output) core. The conceptual diagram is shown in Figure 8.5.

Part III shows how to design an array of MMIO cores for the peripherals on the Nexys 4 DDR prototyping board, including a PWM (pulse width modulation) core, a debouncing core, a seven-segment LED core, a Xilinx XADC controller core, an SPI core, an I<sup>2</sup>C core, a PS2 core, and a music synthesis module with a DDFS (direct digital frequency synthesis) core and an ADSR (attack-decay-sustain-release) envelope core. Part IV discusses the video subsystem framework and covers construction of relevant IP cores.

#### 8.7 BIBLIOGRAPHIC NOTES

Embedded systems encompass a spectrum of design issues. The two books, *Embedded System Design: A Unified Hardware/Software Introduction* by F. Vahid and T. D. Givargis and *Computers as Components: Principles of Embedded Computing System Design, 2nd edition*, by W. Wolf, provide a comprehensive discussion. Software-hardware co-design is an emerging research area. *A Practical Introduction*

Figure 8.5 Vanilla FPro system.

to  $Hardware/Software\ Codesign$  by P. R. Schaumont addresses the basic concepts and issues of combining hardware and software into a single system.

# **Amplifier Transistors**

# **NPN Silicon**

#### **Features**

• These are Pb-Free Devices\*

#### **MAXIMUM RATINGS** (T<sub>A</sub> = 25°C unless otherwise noted)

| Characteristic                                                        | Symbol                            | Value          | Unit        |

|-----------------------------------------------------------------------|-----------------------------------|----------------|-------------|

| Collector - Emitter Voltage                                           | V <sub>CEO</sub>                  | 40             | Vdc         |

| Collector - Base Voltage                                              | V <sub>CBO</sub>                  | 75             | Vdc         |

| Emitter – Base Voltage                                                | V <sub>EBO</sub>                  | 6.0            | Vdc         |

| Collector Current – Continuous                                        | I <sub>C</sub>                    | 600            | mAdc        |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C | P <sub>D</sub>                    | 625<br>5.0     | mW<br>mW/°C |

| Total Device Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C    | P <sub>D</sub>                    | 1.5<br>12      | W<br>mW/°C  |

| Operating and Storage Junction<br>Temperature Range                   | T <sub>J</sub> , T <sub>stg</sub> | -55 to<br>+150 | °C          |

#### THERMAL CHARACTERISTICS

| Characteristic                          | Symbol          | Max  | Unit |

|-----------------------------------------|-----------------|------|------|

| Thermal Resistance, Junction to Ambient | $R_{\theta JA}$ | 200  | °C/W |

| Thermal Resistance, Junction to Case    | $R_{\theta JC}$ | 83.3 | °C/W |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### ON Semiconductor®

#### http://onsemi.com

#### **MARKING DIAGRAM**

A = Assembly Location

Y = Year WW = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

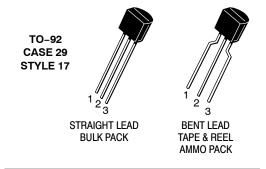

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| P2N2222AG    | TO-92<br>(Pb-Free) | 5000 Units/Bulk       |

| P2N2222ARL1G | TO-92<br>(Pb-Free) | 2000/Tape & Ammo      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# $\textbf{ELECTRICAL CHARACTERISTICS} \ (T_A = 25^{\circ}\text{C unless otherwise noted})$

| Characteristic                                                                                                                                                                                   | Symbol                | Min                                     | Max                          | Unit               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------|------------------------------|--------------------|

| OFF CHARACTERISTICS                                                                                                                                                                              |                       | •                                       |                              | •                  |

| Collector – Emitter Breakdown Voltage<br>(I <sub>C</sub> = 10 mAdc, I <sub>B</sub> = 0)                                                                                                          | V <sub>(BR)</sub> CEO | 40                                      | -                            | Vdc                |

| Collector – Base Breakdown Voltage ( $I_C = 10 \mu Adc, I_E = 0$ )                                                                                                                               | V <sub>(BR)CBO</sub>  | 75                                      | -                            | Vdc                |

| Emitter – Base Breakdown Voltage ( $I_E = 10 \mu Adc, I_C = 0$ )                                                                                                                                 | V <sub>(BR)EBO</sub>  | 6.0                                     | _                            | Vdc                |

| Collector Cutoff Current (V <sub>CE</sub> = 60 Vdc, V <sub>EB(off)</sub> = 3.0 Vdc)                                                                                                              | I <sub>CEX</sub>      | -                                       | 10                           | nAdc               |

| Collector Cutoff Current                                                                                                                                                                         | Ісво                  | _<br>_                                  | 0.01<br>10                   | μAdc               |

| Emitter Cutoff Current (V <sub>EB</sub> = 3.0 Vdc, I <sub>C</sub> = 0)                                                                                                                           | I <sub>EBO</sub>      | -                                       | 10                           | nAdc               |

| Collector Cutoff Current (V <sub>CE</sub> = 10 V)                                                                                                                                                | ICEO                  | _                                       | 10                           | nAdc               |

| Base Cutoff Current<br>(V <sub>CE</sub> = 60 Vdc, V <sub>EB(off)</sub> = 3.0 Vdc)                                                                                                                | I <sub>BEX</sub>      | _                                       | 20                           | nAdc               |

| ON CHARACTERISTICS                                                                                                                                                                               | <u> </u>              | ı                                       | I                            | I                  |

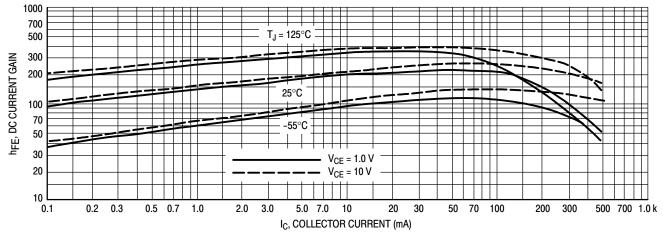

| DC Current Gain                                                                                                                                                                                  | h <sub>FE</sub>       | 35<br>50<br>75<br>35<br>100<br>50<br>40 | -<br>-<br>-<br>300<br>-<br>- | -                  |

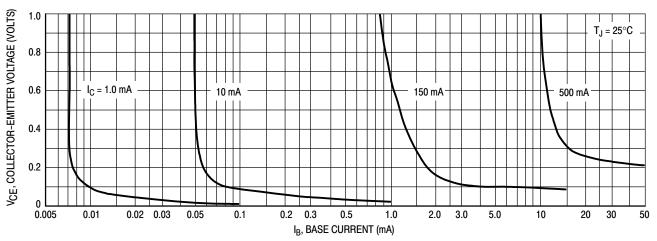

| Collector – Emitter Saturation Voltage (Note 1)<br>( $I_C$ = 150 mAdc, $I_B$ = 15 mAdc)<br>( $I_C$ = 500 mAdc, $I_B$ = 50 mAdc)                                                                  | V <sub>CE(sat)</sub>  | _<br>_<br>_                             | 0.3<br>1.0                   | Vdc                |

| Base – Emitter Saturation Voltage (Note 1)<br>( $I_C$ = 150 mAdc, $I_B$ = 15 mAdc)<br>( $I_C$ = 500 mAdc, $I_B$ = 50 mAdc)                                                                       | V <sub>BE(sat)</sub>  | 0.6                                     | 1.2<br>2.0                   | Vdc                |

| SMALL-SIGNAL CHARACTERISTICS                                                                                                                                                                     | 1                     | 1                                       | I                            | ·I                 |

| Current – Gain – Bandwidth Product (Note 2)<br>(I <sub>C</sub> = 20 mAdc, V <sub>CE</sub> = 20 Vdc, f = 100 MHz)C                                                                                | f <sub>T</sub>        | 300                                     | _                            | MHz                |

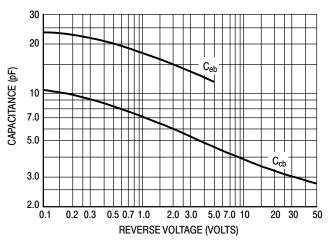

| Output Capacitance (V <sub>CB</sub> = 10 Vdc, I <sub>E</sub> = 0, f = 1.0 MHz)                                                                                                                   | C <sub>obo</sub>      | -                                       | 8.0                          | pF                 |

| Input Capacitance (V <sub>EB</sub> = 0.5 Vdc, I <sub>C</sub> = 0, f = 1.0 MHz)                                                                                                                   | C <sub>ibo</sub>      | -                                       | 25                           | pF                 |

| Input Impedance $ \begin{array}{l} \text{(I}_{C}=\text{1.0 mAdc, V}_{CE}=\text{10 Vdc, f}=\text{1.0 kHz)} \\ \text{(I}_{C}=\text{10 mAdc, V}_{CE}=\text{10 Vdc, f}=\text{1.0 kHz)} \end{array} $ | h <sub>ie</sub>       | 2.0<br>0.25                             | 8.0<br>1.25                  | kΩ                 |

| Voltage Feedback Ratio                                                                                                                                                                           | h <sub>re</sub>       | -<br>-                                  | 8.0<br>4.0                   | X 10 <sup>-4</sup> |

| Small–Signal Current Gain                                                                                                                                                                        | h <sub>fe</sub>       | 50<br>75                                | 300<br>375                   | -                  |

| Output Admittance                                                                                                                                                                                | h <sub>oe</sub>       | 5.0<br>25                               | 35<br>200                    | μMhos              |

| Collector Base Time Constant (I <sub>E</sub> = 20 mAdc, V <sub>CB</sub> = 20 Vdc, f = 31.8 MHz)                                                                                                  | rb′C <sub>c</sub>     | -                                       | 150                          | ps                 |

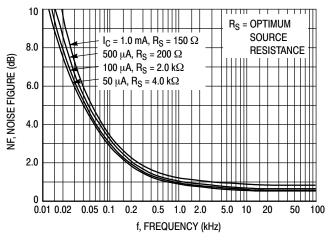

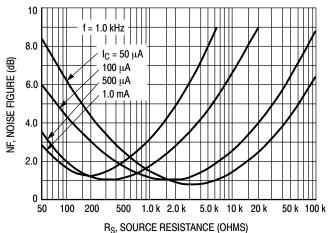

| Noise Figure (I_C = 100 $\mu$ Adc, V <sub>CE</sub> = 10 Vdc, R <sub>S</sub> = 1.0 k $\Omega$ , f = 1.0 kHz)                                                                                      | N <sub>F</sub>        | _                                       | 4.0                          | dB                 |

<sup>1.</sup> Pulse Test: Pulse Width  $\leq$  300  $\mu$ s, Duty Cycle  $\leq$  2.0%. 2. f<sub>T</sub> is defined as the frequency at which  $|h_{fe}|$  extrapolates to unity.

# **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C unless otherwise noted) (Continued)

|                           | Symbol                                                                 | Min            | Max | Unit |    |

|---------------------------|------------------------------------------------------------------------|----------------|-----|------|----|

| SWITCHING CHARACTERISTICS |                                                                        |                |     |      |    |

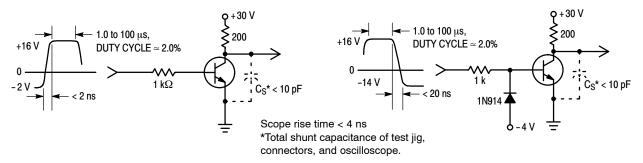

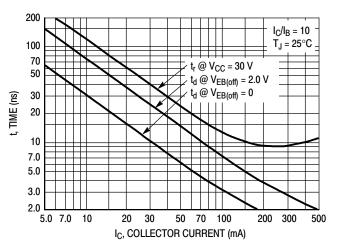

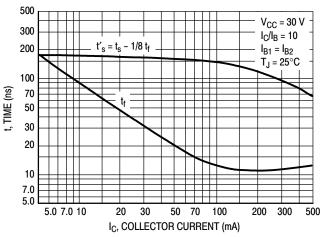

| Delay Time                | $(V_{CC} = 30 \text{ Vdc}, V_{BE(off)} = -2.0 \text{ Vdc},$            | t <sub>d</sub> | -   | 10   | ns |

| Rise Time                 | $I_C = 150 \text{ mAdc}, I_{B1} = 15 \text{ mAdc}) \text{ (Figure 1)}$ | t <sub>r</sub> | -   | 25   | ns |

| Storage Time              | (V <sub>CC</sub> = 30 Vdc, I <sub>C</sub> = 150 mAdc,                  | t <sub>s</sub> | -   | 225  | ns |

| Fall Time                 | $I_{B1} = I_{B2} = 15 \text{ mAdc}$ (Figure 2)                         | t <sub>f</sub> | _   | 60   | ns |

# **SWITCHING TIME EQUIVALENT TEST CIRCUITS**

Figure 1. Turn-On Time

Figure 2. Turn-Off Time

Figure 3. DC Current Gain

Figure 4. Collector Saturation Region

Figure 5. Turn-On Time

Figure 6. Turn-Off Time

Figure 7. Frequency Effects

Figure 8. Source Resistance Effects

500

+0.5

$f_{\mathrm{T}}$ , CURRENT-GAIN BANDWIDTH PRODUCT (MHz) V<sub>CE</sub> = 20 V  $T_J = 25^{\circ}C$ 300 200 100 70 50 1.0 2.0 5.0 7.0 10 70 100 I<sub>C</sub>, COLLECTOR CURRENT (mA)

Figure 9. Capacitances

Figure 10. Current-Gain Bandwidth Product

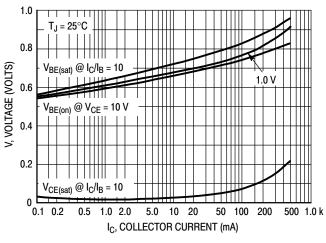

Figure 11. "On" Voltages

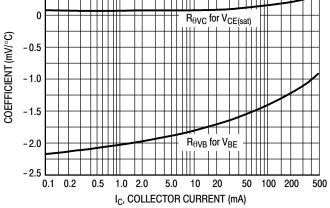

Figure 12. Temperature Coefficients

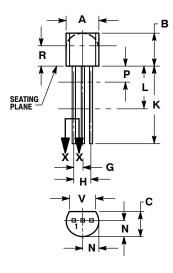

#### PACKAGE DIMENSIONS

TO-92 (TO-226) CASE 29-11 **ISSUE AM**

STRAIGHT LEAD **BULK PACK**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: INCH.

- CONTOUR OF PACKAGE BEYOND DIMENSION R

- IS UNCONTROLLED.

LEAD DIMENSION IS UNCONTROLLED IN P AND BEYOND DIMENSION K MINIMUM.

|     | INCHES |       | MILLIN | ETERS |

|-----|--------|-------|--------|-------|

| DIM | MIN    | MAX   | MIN    | MAX   |

| Α   | 0.175  | 0.205 | 4.45   | 5.20  |

| В   | 0.170  | 0.210 | 4.32   | 5.33  |

| С   | 0.125  | 0.165 | 3.18   | 4.19  |

| D   | 0.016  | 0.021 | 0.407  | 0.533 |

| G   | 0.045  | 0.055 | 1.15   | 1.39  |

| Н   | 0.095  | 0.105 | 2.42   | 2.66  |

| J   | 0.015  | 0.020 | 0.39   | 0.50  |

| K   | 0.500  |       | 12.70  |       |

| L   | 0.250  |       | 6.35   |       |

| N   | 0.080  | 0.105 | 2.04   | 2.66  |

| P   | -      | 0.100 |        | 2.54  |

| R   | 0.115  |       | 2.93   |       |

| V   | 0.135  |       | 3.43   |       |

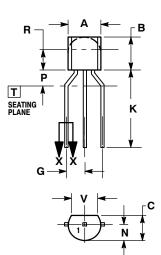

**BENT LEAD TAPE & REEL** AMMO PACK

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- ASME Y14-3M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

CONTOUR OF PACKAGE BEYOND

DIMENSION R IS UNCONTROLLED.

LEAD DIMENSION IS UNCONTROLLED IN P

AND BEYOND DIMENSION K MINIMUM.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN MAX     |      |  |  |

| Α   | 4.45        | 5.20 |  |  |

| В   | 4.32        | 5.33 |  |  |

| С   | 3.18        | 4.19 |  |  |

| D   | 0.40        | 0.54 |  |  |

| G   | 2.40        | 2.80 |  |  |

| J   | 0.39        | 0.50 |  |  |

| K   | 12.70       |      |  |  |

| N   | 2.04        | 2.66 |  |  |

| Р   | 1.50        | 4.00 |  |  |

| R   | 2.93        |      |  |  |

| ٧   | 3.43        |      |  |  |

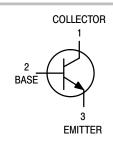

STYLE 17:

PIN 1. COLLECTOR

BASE

**EMITTER**

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, ON Semiconductor and a are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other infellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, super shall indemnify and hold SCILC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILC was negligent regarding the design or manufacture of the part. SCILC is an Equal Opportunity/Affirmative Act

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# UNIVERSIDAD PRIVADA DE TACNA

# FACULTAD DE INGENIERIA ESCUELA PROFESIONAL DE INGENIERIA ELECTRÓNICA

# "PERFIL DE UN INVERNADERO PARA EL FUNDO DE LA UPT"

Presentado por:

Cándido Molanes Miovich

Código: 2012042251

Tacna- Perú

2018

#### Perfil del proyecto

#### 1. Introducción

# 2. Diagnóstico y descripción del problema que se desea enfrentar (1 página)

Retrocedamos 20 años en el tiempo, la zona de agricultura en Tacna ocupaba una fracción del valle del rio Caplina. Actualmente en el año 2018, los terrenos de cultivo van expandiéndose cada vez más, se extienden hasta llegar a terrenos cercanos al litoral. Los mayores problemas que se presentan son la escasez de agua por los cambios climáticos y el uso deficiente del recurso hídrico, por el uso de métodos precarios (riego por surcos, inundación). Un agricultor está acostumbrado a regar y fertilizar manualmente 3 veces a la semana sus plantas, lo que termina en un desperdicio de agua y fertilizantes.

Pocos propietarios de estas tierras usan invernaderos, los cuales empelan dos métodos distintos: como viveros, para cultivar todo tipo de plantas hasta que alcanzan el estado adecuado para su trasplante, distribución y venta (etapa de semilla a plantín), con un uso de todo el año, y como invernadero para cultivar algunos tipos de plantas hasta alcanzar una producción determinada (etapa de semilla a fruto), con un uso de 9 meses, ya que los 3 meses de verano prefiere cultivar en el exterior, por el costo elevado de bajar la temperatura, lo cual está comprobado hasta el momento que no es rentable utilizar un control de temperatura. Cabe resaltar que es vital monitorear la temperatura y humedad ambiental por el problema de garuas esporádicas durante el año.

Ambos métodos de cultivo interno e externo tienen una tecnología de riego, que está muy limitada a un programador de riego de alto costo el cual es programado por un ingeniero agrónomo para regar en determinados horarios. Dependiendo de la evaporación, temperatura promedio, vientos, etc. Extraen mediante estadística cuantos minutos deben regar el cultivo, lo cual no tiene el rendimiento óptimo.

Tomando en cuenta estas consideraciones en conjunto a la falta de capacitación de los agricultores han logrado una baja productividad no solo de tomate sino de otros productos agrícolas en la ciudad, sobre todo esto se ve en la época de invierno, en la cual algunos propietarios no son capaces de producir y otros no logran cubrir la demanda de exportación.

Las condiciones meteorológicas están en constante cambio, afectando la agricultura en Tacna y el mundo. Sin medidas prioritarias, muchas personas están en riesgo de padecer hambre, nuevas formas de cultivar son más necesarias que nunca.

# 3. Resumen (propuesta)

Antes de empezar con la propuesta se hicieron preguntas a un experto con más de 15 años de experiencia en invernaderos en Tacna.

# ¿Qué tipo de perfil externo de invernadero se utiliza en la ciudad de Tacna?

Se utiliza un invernadero tipo capilla a dos aguas con una malla antiáfida, no hay discusión de querer poner uno de plástico o vidrio.

# ¿Cuáles son los parámetros más importantes y dentro de que rango se deben manejar en Tacna?

El parámetro más importante es la humedad del suelo de las plantas. Los parámetros de temperatura, humedad ambiental se usa como referencia para calcular aproximadamente cuanto va a consumir de agua la planta y para resolver cualquier inconveniente temporal de lluvias esporádicas.

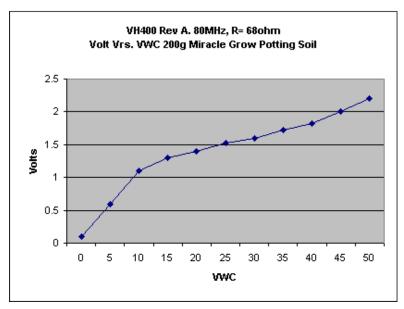

| Variable                                           | Definición<br>conceptual                                               | Indicadores                                              |

|----------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|

| Temperatura<br>(Monitorear)                        | Grado o nivel<br>térmico del<br>invernadero<br>Grado o nivel           | 13-30°C                                                  |

| Humedad relativa<br>(Monitorear)                   | Cantidad de agua<br>en el aire del<br>invernadero en<br>forma de vapor | 60-80%                                                   |

| Humedad del<br>suelo<br>(Monitorear y<br>controlar | Cantidad de agua<br>por volumen de<br>tierra que hay en<br>el cultivo  | 20-25 (VWC) (Dependiendo altura de la base de la planta) |

# ¿En qué momento se activa el riego, se debería regar las 24 horas del día?

Normalmente las plantas se alimentan de 6am - 6pm, y durante ese lapso de tiempo se debe activar las veces que necesite la planta alimentarse, el actuador debe fertirrigar cuantas veces lo necesite.

En consecuencia, ante lo mencionado anteriormente se propone:

Mezclar el agua y fertilizantes en un tanque, para luego suministrarlo a la planta en base a un sensor que nos indique si necesita o no agua.

Monitorear la temperatura y humedad ambiental del invernadero mediante un solo sensor que mide ambos parámetros.

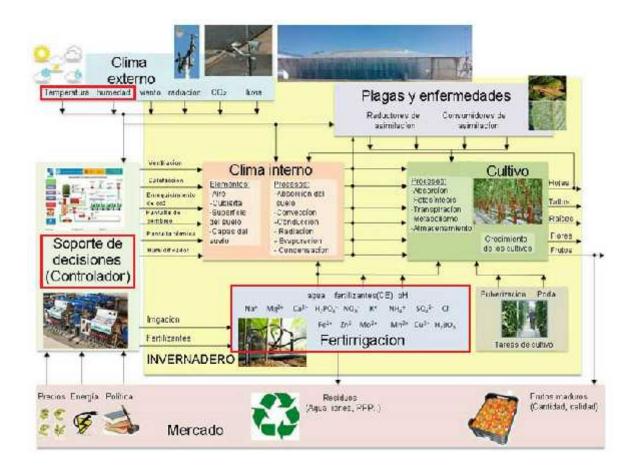

A continuación, se muestra el flujo que habrá en el invernadero.

Fig. 1. "Diagrama conceptual de la producción en invernadero."

#### Monitoreo de temperatura

Una planta de tomate no soporta el frio ni tampoco el calor, por lo que las temperaturas por debajo de 10°C y por encima de 35°C impedirán y reducirán el desarrollo de frutos.

La planta de tomate tiene un crecimiento normal y un buen desarrollo de frutos cuando su clima es cálido con una temperatura diurna de 21-29,5°C y una nocturna de 18,5-21°C

#### Monitoreo de humedad ambiental

La cantidad de vapor de agua en el aire del interior del invernadero es medida en porcentaje por la humedad relativa, esta no es una variable climática que influya directamente al crecimiento del cultivo, aunque su control es de peculiar interés. Pero

para evitar la aparición y desarrollo de enfermedades fúngicas es necesario que la humedad relativa se mantenga entre 60 y 80%.

# Sensor propuesto para temperatura y humedad

Pmod HYGRO: Sensor de temperatura y humedad digital

Costo: s/55

#### Control de humedad del suelo

La medición de humedad del suelo se basa en la medición de contenido volumétrico de agua (vwc) o potencial matricial del suelo. Para fijar un control sobre la humedad del suelo, debemos determinar el contenido de humedad.

# Sensor propuesto

Watermark 200ss

Costo: s/300

**Actuador propuesto**

# Electrovalvula Burket 1/2'

Costo: S/300 soles

# **Controlador propuesto**

FPGA nexys 4

Costo: Gratis en la escuela se cuenta con 4

# 4. Descripción general (Invernadero en el fundo dimensiones del invernadero amalsicos.

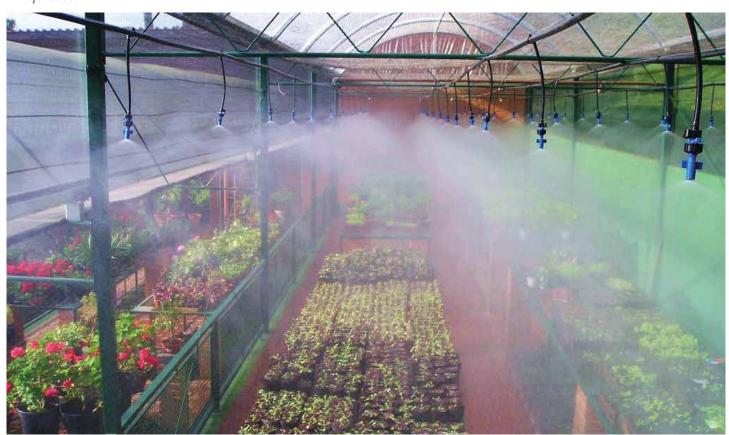

Se implementará 1 invernadero tipo capilla a dos aguas para el cultivo de almácigos con un sistema de aspersión, previsto para suministrar el agua y fertilizantes en toda la superficie en 4 turnos, con 2 electroválvulas en campo, de acuerdo a la lectura de un sensor de humedad de suelo. Se contará con un sensor de monitoreo de temperatura y humedad ambiental. Todo esto tiene un soporte de decisiones quien se encarga de controlar y regular la fertirigación.

#### **Esctructura**

Las medidas son:

Ancho: 7m Largo: 15m

5. Presupuesto Pino S.A.C. (Sistema de riego) y IMATEC(Estructura y malla)

# COTIZACION N°. CT1-162068

Pag.

1

4,743.63

5,597.48

853.85

SEÑORES: UNIVERSIDAD PRIVADA DE TACNA

**FECHA:** 02/10/2018

REF:

ATENCION:

Es grato el dirigirnos a ustedes con la finalidad de alcanzarles nuestra cotización por lo siguiente:

|    | CODIGO    | DESCRIPCION                                             | CANT. | UND. | V. VENTA<br>S/ | VALOR TOTAL<br>S/ |

|----|-----------|---------------------------------------------------------|-------|------|----------------|-------------------|

| 1  |           | plantinera                                              |       |      | 0.00           | 0.00              |

| 2  | 208500104 | ELECTROBOMBA CONFORTO 1 HP INOX 220V-60Hz // NPXM100GIR | 1     | u.   | 920.00         | 920.00            |

| 3  | 121200300 | TERMINAL MIXTO MACHO PVC 32 X 40 X 1"                   | 10    | u.   | 2.00           | 20.00             |

| 4  | 106100800 | CODO 90º PE 32 MM                                       | 2     | u.   | 4.00           | 8.00              |

| 5  | 110200300 | FILTRO 1" DISCO 130 MIC ROSCADO AZUD                    | 1     | u.   | 75.00          | 75.00             |

| 6  | 114000400 | MANGUITO PVC MIXTO 32 X 1"                              | 3     | u.   | 5.00           | 15.00             |

| 7  | 1011094   | VALVULA ENLACE R/HEMBRA 1"                              | 4     | u.   | 35.00          | 140.00            |

| 8  | 222500111 | TUBO HID PVC 32 MM C-10                                 | 4     | Tb.  | 48.00          | 192.00            |

| 9  | 109501100 | ENLACE R/H PE 32 X 1                                    | 3     | u.   | 3.00           | 9.00              |

| 10 | 206200111 | CODO 90º PVC SOLDABLE 32MM                              | 9     | u.   | 4.00           | 36.00             |

| 11 | 221000111 | TEE SOLDABLE 32MM                                       | 2     | u.   | 9.00           | 18.00             |

| 12 | 120400800 | TAPON FINAL PE 32 MM                                    | 2     | u.   | 4.00           | 8.00              |

| 13 | 109502000 | ENLACE R/M PE 20 X 3/4"                                 | 3     | u.   | 3.00           | 9.00              |

| 14 | 118000900 | REDUCCION MACHO/HEMBRA PE 1" X 3/4"                     | 3     | u.   | 2.00           | 6.00              |

| 15 | 213500209 | MANGUERA CIEGA 20MM X 1.30 ESP X 300 MTS                | 0.50  | rol  | 245.00         | 122.50            |

| 16 | 115100500 | NEBULIZADOR GREEN MIST 30 LPH AZUL                      | 100   | u.   | 12.00          | 1,200.00          |

| 17 | 120400600 | TAPON FINAL PE 20MM                                     | 3     | u.   | 2.00           | 6.00              |

| 18 | 115700700 | PEGAMENTO PVC 1/4 WELDALL                               | 1     | u.   | 33.00          | 33.00             |

| 19 | 205600201 | CINTA TEFLON 19MM 50MTS                                 | 1     | u.   | 20.00          | 20.00             |

| 20 |           | tablerro electrico de proteccion                        | 1     | u.   | 850.00         | 850.00            |

| 21 | 207800109 | DEPOSITO P.E NEGRO X 1500 LTS.                          | 1     | u.   | 1,800.00       | 1,800.00          |

| 22 | 115500100 | PASAMUROS PVC 1"                                        | 1     | u.   | 95.00          | 95.00             |

| 23 | 114000400 | MANGUITO PVC MIXTO 32 X 1"                              | 3     | u.   | 5.00           | 15.00             |

**CONDICIONES DE VENTA:**Forma de Pago : CONTADO

Validez de la Oferta : 0 dias Lugar de Entrega

Los precios unitarios Incluyen IGV Valor Venta S/ IGV 18% S/ Precio de Venta S/

**CUENTA CORRIENTE**

540-1787227-0-41 SOLES BCP-Tacna 540-1773486-1-53 DOLARES BCP - Tacna

0011-0232-01-00072868 SOLES BBVA - Tacna 0011-0232-01-00072876 DOLARES BBVA - Tacna 000-7683944 SOLES SCOTIABANK - TACNA 000-3574714 DOLARES SCOTIABANK - TACNA

0151-072070 DETRACCIONES BCO. DE LA NACION

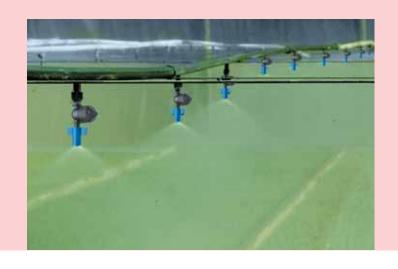

# **GREEN MIST**

Emisor de doble propósito para nebulizar y regar sobre mesas de propagación

# **CARACTERÍSTICAS PRINCIPALES**

- Gran uniformidad de cobertura

- Tamaño ideal de gotitas para optimizar la dispersión de la fina neblina

- Ausencia de goteo durante el funcionamiento

- Distribución simétrica del riego y sin discontinuidad (sin deflexión y sin zonas "muertas")

- Elemento antidrenante (LPD) para un perfecto funcionamiento en pulsos

- Bajo costo

# **CARACTERÍSTICAS TÉCNICAS**

• Presión: 2.0 a 3.5 bar

• Caudal: 30 - 40 l/h (ver tabla)

• Requisitos de filtrado: 120 mesh (130 micrones)

• Diámetro de humedecimiento: I.2 m

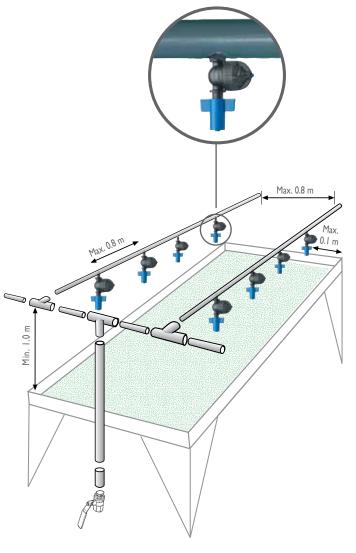

# **INSTRUCCIONES DE INSTALACIÓN**

• Altura de las unidades por encima de las mesas: 1.0 - 1.2 m

• Espaciamiento máximo entre unidades sobre el lateral: 0.8 m

• Espaciamiento máximo entre laterales: 0.8 m

• Distancia máxima del lateral desde el borde del banco: 0.1 m

| CAUDALES Y PRESIONES |     |     |     |     |  |

|----------------------|-----|-----|-----|-----|--|

| Presión (bar)        | 2.0 | 2.5 | 3.0 | 3.5 |  |

| Caudal (I/h)         | 30  | 34  | 37  | 40  |  |

# Diseño esquemático de una instalación sobre tuberia de PVC

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

| CLIENTE:        | Universidad Privada de Tacna    |       |          |

|-----------------|---------------------------------|-------|----------|

| UBICACIÓN OBRA: | Fundo de la UPT                 |       |          |

| TLF / E-mail:   | electrónica.transmite@gmail.com | FECHA | 04/10/18 |

# TÚNEL KIT IMATEC

invernaderos • umbráculos • túneles • mesas • climatización • accesorios • invernaderos • umbráculos • túneles • mesas • climatización

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

#### **TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

PAG. 1

# <u>ÍNDICE</u>

- 1. CARACTERÍSTICAS TÉCNICAS

- 2. ESTRUCTURA Y CUBIERTA

- 2.1. ESTRUCTURA

- 2.2. SISTEMA DE SUJECIÓN

- 2.3. PUERTA Y VENTILACIÓN

- 2.4. CIMENTACIÓN

- 2.5. CUBIERTA

- 2.6. CALIDAD DEL ACERO

- 2.7. GALVANIZADO

- 3. PRESUPUESTO

- 3.1. DESCRIPCIÓN DE LA ESTRUCTURA Y OFERTA ECONÓMICA

- 3.2. CONCEPTOS NO INCLUIDOS EN LA OFERTA

- 3.3. FORMA DE PAGO

- 3.4. PLAZO DE ENTREGA

- 4. PLANOS

- 5. FOTOS

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

DEPARTAMENTO COMERCIAL

PAG. 2

# 1.- CARACTERÍSTICAS TÉCNICAS

# 2.- ESTRUCTURA Y CUBIERTA

#### 2.1.- ESTRUCTURA

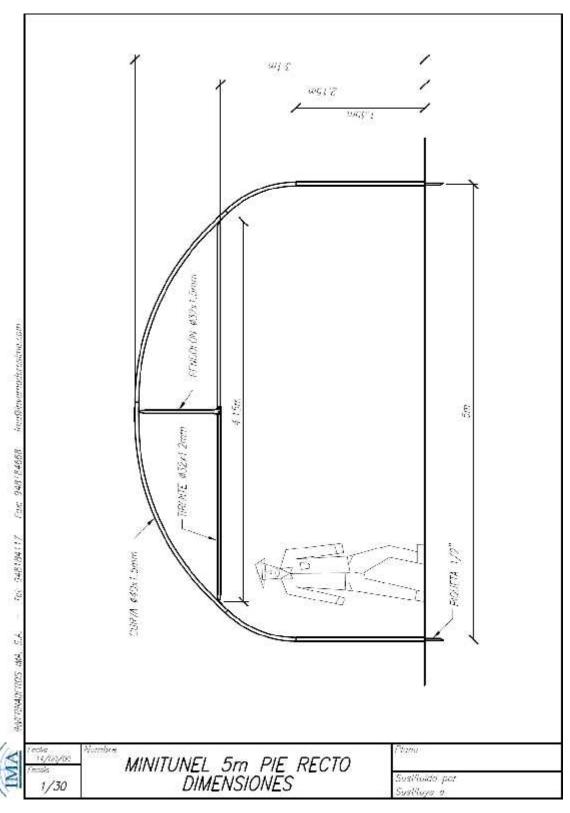

Arcos de tubo de diámetro 40 mm y 1,5 mm de espesor, colocados cada 2 m. Anclados sobre piquetas clavadas directamente al suelo.

- Tirantes y pendolones de tubo redondo de 32 mm de diámetro y 1,2 mm de espesor. Se coloca un tirante y pendolón cada arco. El tirante es uno de los elementos más importantes en el correcto arriostramiento del invernadero

- El tirante sirve como **soporte de cultivo**, para ello se ha dotado de un refuerzo vertical, el pendolón, que evita el desplazamiento del plano recto del tirante.

- Altura a la cumbrera 3 m

- Altura al tirante 2 m.

# 2.2. – SISTEMA DE SUJECIÓN

**5 Correas longitudinales de** tubo de 32 mm de diámetro y 1,2 mm de espesor. Permiten amarrar los arcos entre sí de manera que trabajan a tracción y contracción para la correcta sujeción de la estructura.

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

DEPARTAMENTO COMERCIAL

PAG. 3

- 5 Refuerzos frontales de arco a arco en cada extremo completan el arriostramiento del invernadero.

- Tornillería, todas las uniones están previstas para facilitar el montaje y desmontaje de sus elementos con la mayor facilidad y fiabilidad. Tornillos y tuercas hexagonales DIN-933 y DIN-934 en calidad comercial 5.6, correspondiendo a las designaciones F-7417, según Norma UNE-36-089-72. Resistencia media a la tracción 55 Kg/mm².

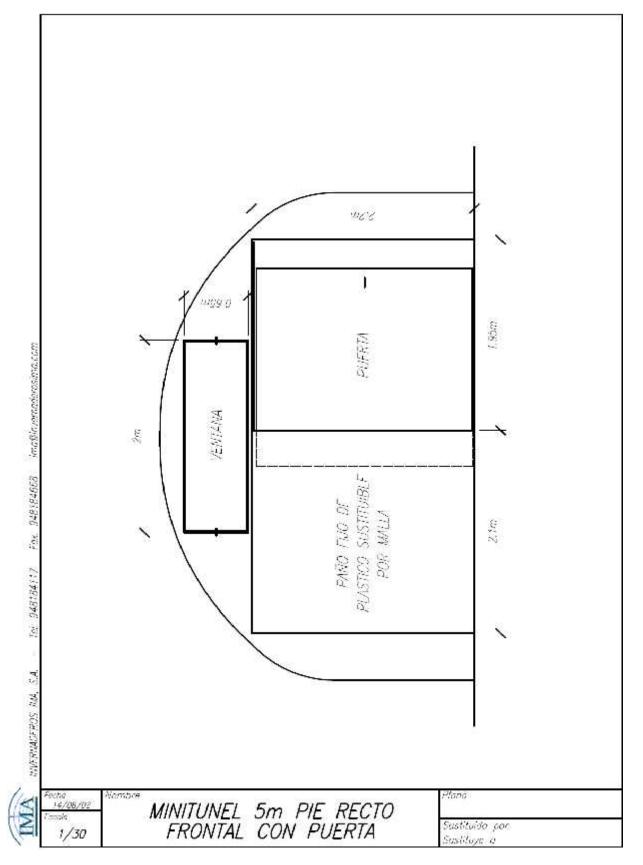

# 2.3.- PUERTA Y VENTILACIÓN

2 Puertas Correderas, colocadas una en cada frontal de dimensiones 2x2 m. Disponen de un paño fijo que se puede cubrir con plástico o con malla para mejorar la ventilación.

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

PAG. 4

2 Ventanas frontales abatibles de dimensiones 2 x 0,6 m. Colocadas en la media luna del invernadero. Incorporan pestillo para un cierre adecuado.

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

DEPARTAMENTO COMERCIAL

PAG. 5

#### 2.4.- CIMENTACIÓN

La estructura no requiere cimentación, lo que facilita y agiliza el montaje. El plástico enterrado en 2 zanjas paralelas al invernadero y cubierto de tierra sujeta fuertemente la estructura al suelo.

#### 2.5.- CUBIERTA

Material de cubierta **plástico térmico** de **800gg** (0,2 mm).

**Garantía**: 48 meses en el norte de España y 36 en el sur

Termicidad: >al 86%

Trasmisión luminosa global: > 92%

**12 líneas de monofilamento** sujetas en los extremos mantienen el plástico tenso y evitan la formación de bolsas de agua.

#### 2.6.- CALIDAD DEL ACERO

Todo el acero que se utiliza en los invernaderos IMA como materia prima es de probada calidad y homogeneidad y ha sido seleccionado en las mejores acerías europeas.

Para la realización de todo tipo de tubos, se parte de fleje comercial, el cual debe poderse plegar, su resistencia máxima no debe pasar de 41-42 Kg/mm². La resistencia media del material empleado es de 35-36 Kg/mm², se puede equiparar con Rst-34.

Hay que tener en cuenta que en todo proceso posterior al perfilado para la conformación de los tubos, el material adquiere una resistencia adicional, que mejora sus características, lo cual se ve en los ensayos mecánicos, pero no recogidos en la norma.

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

PAG. 6

#### 2.7.- GALVANIZADO

Todo el material con el que se fabrican los invernaderos IMA, es de Acero galvanizado por Inmersión según el procedimiento Sendzimir. Este proceso consiste en la inmersión en un baño de Zinc a una temperatura específica y constante durante todo el proceso, de chapa de bobina, laminada tanto en frío como en caliente y preparada para el galvanizado con un decapado previo, con lo que se consigue una auténtica fusión entre el acero y el zinc. Este proceso garantiza un recubrimiento de zinc según la norma UNE 36130 y la Euro norma 142-79. Según estas especificaciones el material utilizado es Z-275, con 275 g/m². Con esto se evita cualquier proceso de corrosión.

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

PAG. 7

#### 3.- PLANOS

TLF: 052-314300 Tacna www.criadoylopez.com

**TÚNEL KIT IMATEC**

DEPARTAMENTO COMERCIAL PAG. 8

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

#### **TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

PAG. 9

### 4.- FOTOS

### Marcaje y piquetas

### Ensamblaje arcos, tirantes, pendolones y correas

### **Estructura**

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

PAG. 10

### Cubierta plástico

### Ventana y Puerta

TLF: 052-314300 Tacna 056-720078 Ica

www.criadoylopez.com

**TÚNEL KIT IMATEC**

**DEPARTAMENTO COMERCIAL**

PAG. 11

### 5.- PRESUPUESTO ESTRUCTURA Y MALLA

El presupuesto es de s/7000.

### 6. Presupuesto Final

Pino S.A.C. (Sistema de riego) + IMATEC(Estructura y malla) + Tecnología = **s/13 252.48**

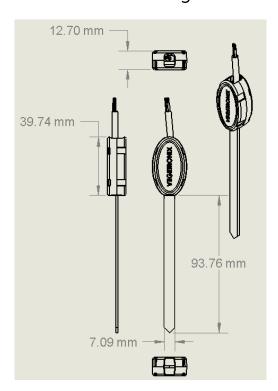

### **Datasheet SHT85**

# **Humidity and Temperature Sensor**

- High-accuracy RH&T sensor for demanding measurement & test applications

- Typical accuracy of  $\pm$  1.5 %RH and  $\pm$  0.1 °C

- Pin-type packaging for easy integration and replacement

- Fully calibrated, linearized, and temperature compensated digital output

#### **Product Summary**

SHT85 is Sensirion's best-in-class humidity sensor with pin-type connector for easy integration and replacement. It builds on a highly accurate and long-term stable SHT3x sensor that is at the heart of Sensirion's new humidity and temperature platform. The unique package design allows for the best possible thermal coupling to the environment and decoupling from potential heat sources on the main board. The SHT85 features a PTFE membrane dedicated to protect the sensor opening from liquids and dust according to IP67, without affecting the response time of the RH signal. It thus allows for sensor use under harsh environmental conditions, (such as spray water and high exposure to dust). Final accuracy testing on product level ensures best performance, making the SHT85 the ultimate choice for even the most demanding applications.

#### Benefits of Sensirion's CMOSens® Technology

- High reliability and long-term stability

- Industry-proven technology with a track record of more than 10 years

- Designed for mass production

- Optimized for lowest cost

- Low signal noise

### Content

| 1 Humidity and Temperature Sensor Specifications | 3  |

|--------------------------------------------------|----|

| 2 Electrical Specifications                      | 6  |

| 3 Pin Assignment                                 | 8  |

| 4 Operation and Communication                    | 9  |

| 5 Packaging                                      | 18 |

| 6 Shipping Package                               | 20 |

| 7 Quality                                        | 21 |

| 8 Ordering Information                           | 22 |

| 9 Further Information                            | 23 |

| 10 Important Notices                             | 24 |

| 11 Revision History                              | 25 |

| 12 Headquarters and Subsidiaries                 | 25 |

Preliminary datasheet

### 1 Humidity and Temperature Sensor Specifications

#### **Relative Humidity**

| Parameter                       | Conditions                              | Value        | Units |

|---------------------------------|-----------------------------------------|--------------|-------|

| Accuracy tolerance <sup>1</sup> | Тур.                                    | ±1.5         | %RH   |

|                                 | Max.                                    | see Figure 1 | -     |

|                                 | Low, typ.                               | 0.21         | %RH   |

| Repeatability <sup>2</sup>      | Medium, typ.                            | 0.15         | %RH   |

|                                 | High, typ.                              | 0.08         | %RH   |

| Resolution                      | Тур.                                    | 0.01         | %RH   |

| Hysteresis                      | At 25°C                                 | ±0.8         | %RH   |

| Specified range <sup>3</sup>    | Non-condensing environment <sup>4</sup> | 0 to 100     | %RH   |

| Response time <sup>5</sup>      | τ 63%                                   | 86           | S     |

| Long-term drift <sup>7</sup>    | Тур.                                    | <0.25        | %RH/y |

Table 1: Humidity sensor specifications

#### **Temperature**

| Parameter                       | Conditions          | Value        | Units |

|---------------------------------|---------------------|--------------|-------|

| Accuracy tolerance <sup>1</sup> | Typ., 20°C to 50 °C | ±0.1         | °C    |

|                                 | Max.                | see Figure 2 | 5     |

|                                 | Low, typ.           | 0.15         | °C    |

| Repeatability <sup>2</sup>      | Medium, typ.        | 0.08         | °C    |

|                                 | High, typ.          | 0.04         | °C    |

| Resolution                      | Тур.                | 0.01         | °C    |

| Operating range                 | -                   | -40 to 1058  | °C    |

| Response time <sup>9</sup>      | τ 63%               | >2           | S     |

| Long-term drift                 | Typ.                | <0.03        | °C/y  |

Table 2: Temperature sensor specifications

<sup>&</sup>lt;sup>1</sup> For definition of typ. and max. accuracy tolerance, please refer to the document "Sensirion Humidity Sensor Specification Statement".

<sup>&</sup>lt;sup>2</sup> The stated repeatability is 3 times the standard deviation (3σ) of multiple consecutive measurement values at constant conditions and is a measure for the noise on the physical sensor output.

<sup>&</sup>lt;sup>3</sup> Specified range refers to the range for which the humidity sensor specification is guaranteed.

<sup>&</sup>lt;sup>4</sup> Condensation shall be avoided because of risk of corrosion and leak currents on the PCB. For details about recommended humidity and temperature operating range, please refer to Section 1.2.

<sup>&</sup>lt;sup>5</sup> Time for achieving 63% of a humidity step function, valid at 25°C and 1 m/s airflow. Humidity response time in the application depends on the design-in of the

$<sup>^{6}</sup>$  With activated ART function (see Section 4.7) the response time can be improved by a factor of 2.

<sup>&</sup>lt;sup>7</sup> Typical value for operation in normal RH/T operating range. Max. value is < 0.5 %RH/y. Value may be higher in environments with vaporized solvents, out-gassing tapes, adhesives, packaging materials, etc. For more details please refer to Handling Instructions.</p>

<sup>&</sup>lt;sup>8</sup> All parts, incl. PCB are rated up to 125°C, except for the connector, which is rated for 105°C.

<sup>&</sup>lt;sup>9</sup> Temperature response time depends on heat conductivity of sensor substrate and design-in of sensor in application.

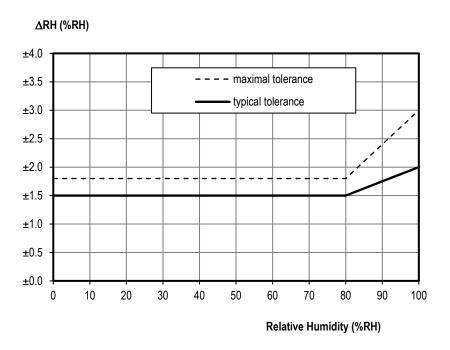

Figure 1: Typical and maximal tolerance for relative humidity in %RH at 25 °C.

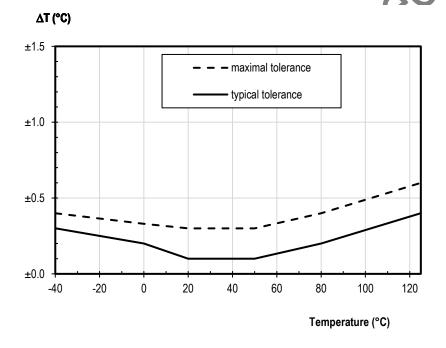

Figure 2: Typical and maximal tolerance for temperature sensor in °C

### 1.1 RH Accuracy at Various Temperatures

Typical RH accuracy at 25°C is defined in Figure 2. For other temperatures, typical accuracy has been evaluated to be as displayed in Figure 4.

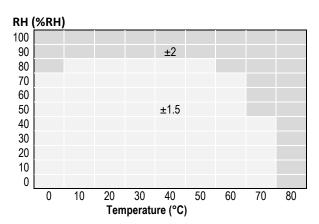

Figure 3: Typical accuracy of relative humidity measurements given in %RH for temperatures 0 – 80°C.

#### 1.2 Recommended Operating Conditions

The sensor shows best performance when operated within recommended normal temperature and humidity range of 5-60 °C and 20-80 %RH, respectively. Long term exposure to conditions outside normal range, especially at high humidity, may temporarily offset the RH signal (e.g. +3%RH after 60h at >80%RH). After returning into the normal temperature and humidity range, the sensor will slowly come back to calibration state by itself. Prolonged exposure to extreme conditions may accelerate ageing.

To ensure stable operation of the humidity sensor, the conditions described in the document "SHTxx Assembly of SMD Packages", Section "Storage and Handling Instructions" regarding exposure to volatile organic compounds have to be met. Please note as well that this does apply not only to transportation and manufacturing, but also to operation of the SHT85.

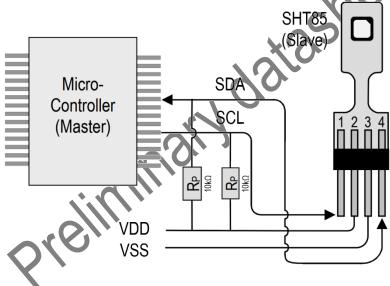

# **2 Electrical Specifications**

#### 2.1 Electrical Characteristics

| Parameter                              | Symbol                | Conditions                                        | Min  | Тур. | Max  | Units | Comments                                                                                                                                                              |

|----------------------------------------|-----------------------|---------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply voltage                         | $V_{DD}$              |                                                   | 2.15 | 3.3  | 5.5  | V     | -                                                                                                                                                                     |

| Power-up/down level                    | $V_{\text{POR}}$      |                                                   | 1.8  | 2.1  | 2.15 | V     | -                                                                                                                                                                     |

| Slew rate change of the supply voltage | V <sub>DD</sub> ,slew |                                                   | -    | -    | 20   | V/ms  | Voltage changes on the VDD line between $V_{\text{DD,min}}$ and $V_{\text{DD,max}}$ should be slower than the maximum slew rate; faster slew rates may lead to reset; |

| Supply current                         | I <sub>DD</sub>       | Idle state<br>(single shot mode)<br>T= 25°C       | -    | 0.2  | 12.0 |       | Current when sensor is not                                                                                                                                            |

|                                        |                       | Idle state<br>(single shot mode)<br>T= 125°C      | -    | -    | 6.0  | μA    | performing a measurement during single shot mode                                                                                                                      |